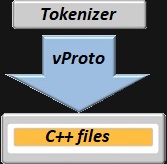

vProto - utilizes a human-perceptible State Machine and generates C++ code based on it to facilitate state transitions when parsing incoming data. It's extremely convenient for parsing existing protocols as well as describing custom ones. It's designed to work with any data fragmentation (data can arrive even byte by byte), which is highly relevant for the TCP protocol.

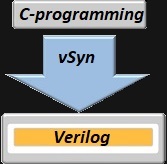

vSyn - transfer (translator) C language to Verilog. The development of algorithms in the C language is significantly simpler, more compact, and faster than in hardware description languages (Verilog, VHDL, SystemC, etc).

An automated process of transferring C logic to the hardware level is a highly effective approach in implementing complex and large projects on PLDs (Programmable Logic Devices) FPGA:

- Time savings on development, testing, and debugging (C code is much easier to debug on x86/64)

- Automated process of forming state machines (Finite State machine)

- Memory interface compatible with the Memory Interface Generator (LogiCORE IP Core from Xilinx)

- Minimization of code size and consequently, reduction of errors

- Ability to not worry about the complexities of Verilog internals

- Code portability, ability to use a replenishable algorithm library: red-black-tree (std::map)

These devices were 100% developed by me, including schematic design in Altium Designer, PCB layout, manual soldering of prototypes, and programming of both FPGA and microcontrollers. The development took place at home, outside of working hours, but later some of these devices were sold and went into mass production